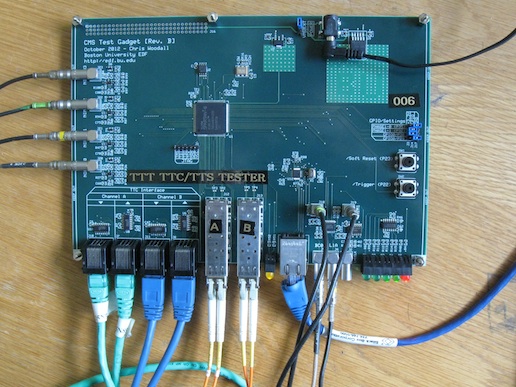

TTT: TTC TTS Tester for CMS and G minus 2

The TTT is a piece of test equipment design for CMS through the BU Electronic Design Facility (EDF). Its main function is to generate L1A (Level-1 Accept) trigger events and stream them to another piece of equipment and listen to that piece of equipment to see if its buffer is full.

The TTT runs a Xilinx Spartan-6 FPGA, with an Ethernet MAC I wrote, and communicates with a PC using a protocol called IPBus. This allows for configurations to be set, such as, running off of an external clock. The board to board communications are done over a fiber optic interface and the Spartan-6 chip decodes an 80MHz BiPhase Mark Coded datastream which multiplexes two datastreams together.

Eric Hazen wrote the VHDL for the internal trigger simulator and Charlie Hill wrote the initial software for interfacing with the TTT over IPBus from a computer.